Difference between revisions of "MC System"

| Line 2: | Line 2: | ||

The many-core version of the project provides different type of tiles, although all share the same network- and coherence-related components. On the networking side, a generic tile of the system features a '''Network Interface''' module and a hardware '''Router''', both described in [[Network|Network architecture]] section. | The many-core version of the project provides different type of tiles, although all share the same network- and coherence-related components. On the networking side, a generic tile of the system features a '''Network Interface''' module and a hardware '''Router''', both described in [[Network|Network architecture]] section. | ||

| − | The nu+ many-core features a shared-memory system, each nu+ core has a private L1 data cache, while the L2 cache is spread all over the instantiated tile | + | The nu+ many-core features a shared-memory system, each nu+ core has a private L1 data cache, while the L2 cache is spread all over the instantiated tile along with a '''Directory Controller''' module which handles and stores coherence information for cached memory lines. This component is further described in [[Coherence|Coherence architecture]] section. |

== NUPLUS tile == | == NUPLUS tile == | ||

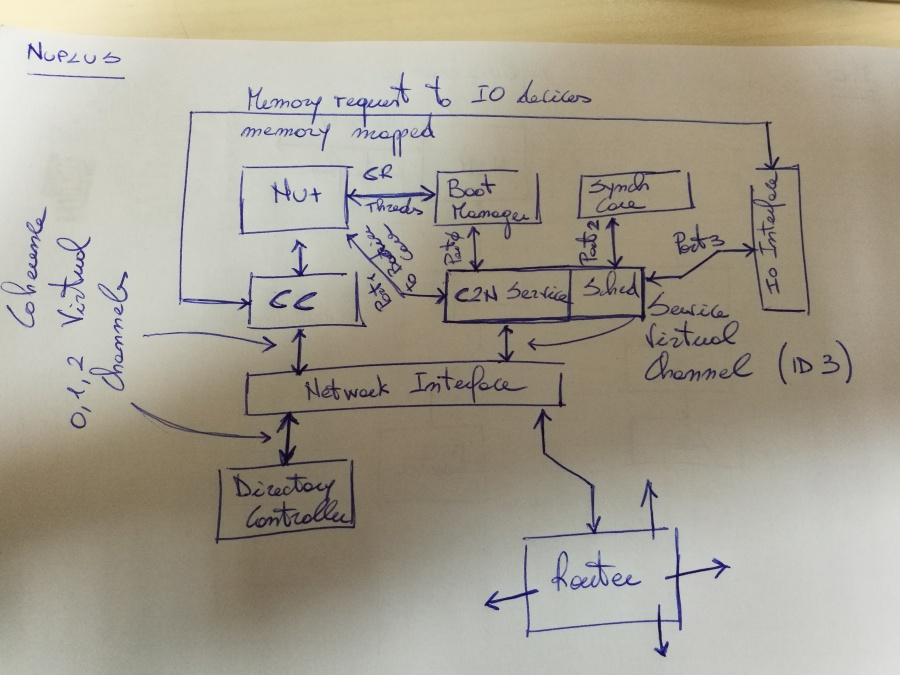

| − | The NUPLUS tile | + | The NUPLUS tile mainly equips a nu+ GPGPU core, described in [[Core|Nu+ GPGPU core]] section, and components used to interface the core with both networking and coherence systems. The following figure depicts an modular view of the NUPLUS tile: |

[[File:NU.jpg|900px]] | [[File:NU.jpg|900px]] | ||

Revision as of 13:18, 17 May 2019

The many-core version of the project provides different type of tiles, although all share the same network- and coherence-related components. On the networking side, a generic tile of the system features a Network Interface module and a hardware Router, both described in Network architecture section.

The nu+ many-core features a shared-memory system, each nu+ core has a private L1 data cache, while the L2 cache is spread all over the instantiated tile along with a Directory Controller module which handles and stores coherence information for cached memory lines. This component is further described in Coherence architecture section.

Contents

NUPLUS tile

The NUPLUS tile mainly equips a nu+ GPGPU core, described in Nu+ GPGPU core section, and components used to interface the core with both networking and coherence systems. The following figure depicts an modular view of the NUPLUS tile:

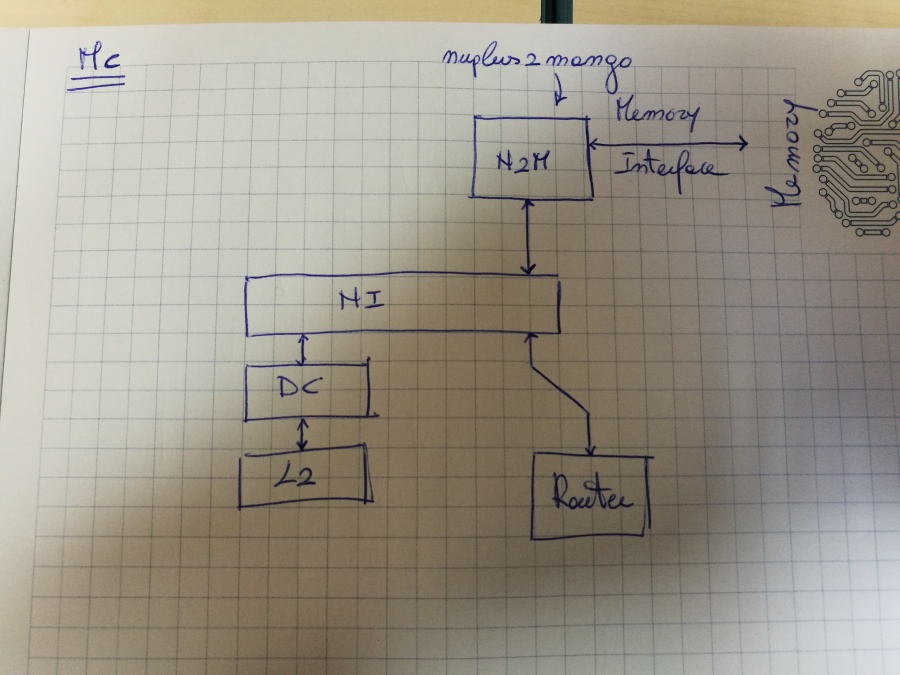

MC tile

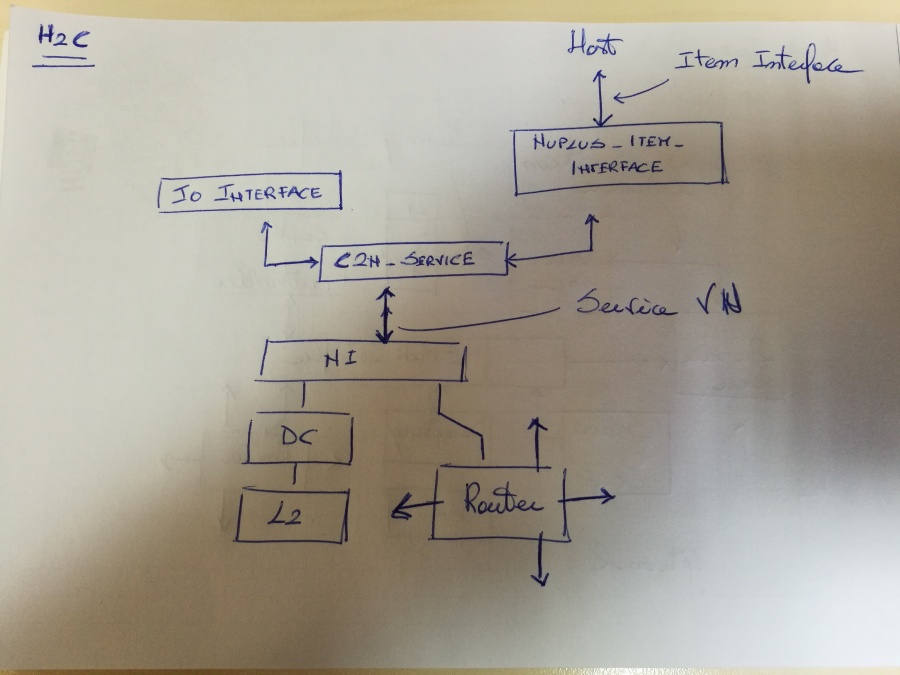

H2C tile

NONE tile

HT tile

Described in Heterogeneous Tile section.