Difference between revisions of "Coherence"

| Line 8: | Line 8: | ||

[[File:high_level_protocol.jpg|800px|high_level_protocol]] | [[File:high_level_protocol.jpg|800px|high_level_protocol]] | ||

| − | Inoltre si specifica che il nostro protocollo è di tipo invalidate; ciò signifca che ogni volta un core modifica un blocco di memoria deve invalidare gli altri al fine di poter garantire che nessun altro core stia leggendo un valore vecchio di tale blocco in modifica. | + | Inoltre si specifica che il nostro protocollo è di tipo invalidate; ciò signifca che ogni volta un core modifica un blocco di memoria deve invalidare gli altri al fine di poter garantire che nessun altro core stia leggendo un valore vecchio di tale blocco in modifica. |

Infine si suppone che le cache siano di tipo write-back. Ciò significa che i dati vengono scritti in cache e verranno poi scritti in memoria solo quando il dato deve essere rimosso dalla cache stessa. | Infine si suppone che le cache siano di tipo write-back. Ciò significa che i dati vengono scritti in cache e verranno poi scritti in memoria solo quando il dato deve essere rimosso dalla cache stessa. | ||

Revision as of 19:47, 20 September 2017

Avendo un sistema many-core in cui ogni core ha una propria cache L1 privata - e condivisa tra i thread - ed una cache L2 distribuita tra le tile, è stato introdotto un sistema di coerenza al fine di poter dare l'apparenza ad un core di avere una singola cache a sua disposizione e di esserne l'unico utilizzatore. Quindi ogni struttura di memorizzazione è affiancata da un controllore di coerenza che manipola i dati e contemporaneamente invia messaggi agli altri controllori di coerenza tramite una rete costituendo un sistema distribuito basato su scambio di messaggi. Una particolare attenzione è stata posta sul disaccoppiamento tra la gestione della coerenza e la gestione del dato all'interno del datapath del core. I core non hanno coscienza del protocollo di coerenza, ma hanno solo una visione dei privilegi sui dati. I dati ed i privilegi sono opportunamente manipolati dall'infrastruttura di coerenza. Il protocollo di coerenza può essere sostanzialmente intercambiabile con altri.

Il nostro sistema di coerenza è basato sull'utilizzo di directory al fine di poter ottenere una migliore scalabilità nei confronti del numero di core nel sistema. Ci sono N tile connesse tra di loro tramite una rete mesh 2D; ogni tile contiene un core nu+ in cui possono girare K thread. In una tile c'è una cache L1 privata - e condivisa tra i thread di un core - ed una cache L2 inclusiva e condivisa tra le varie tile. Il sistema delle directory è distribuito ed una porzione è bufferizzata nella cache associata alla L2: sfruttando l'inclusività della L2, la cache L2 viene legata alla cache della directory.

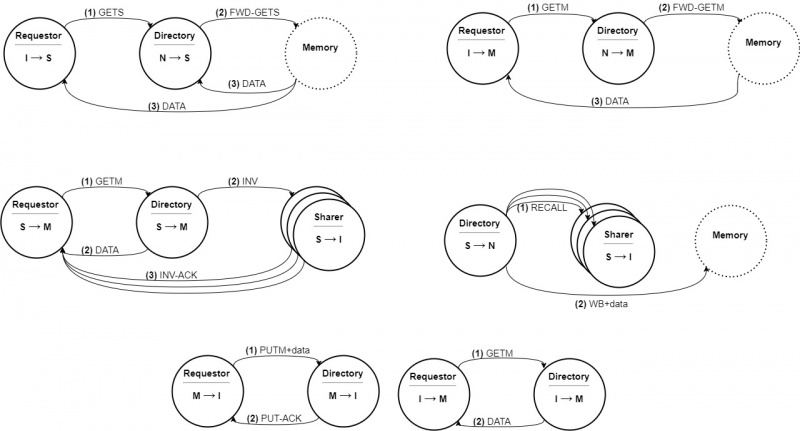

Il protocollo di coerenza per ora sviluppato è una versione modificata dell'MSI, con tre stati stabili per la gestione del livello 1 di cache (Modified, Shared ed Invalid) e quattro stati stabili per il livello 2 (Modified, Shared, Non-Cached ed Invalid). La semantica degli stati è la stessa di quella definita nella letteratura, ad eccezione per lo stato Non-Cached, il quale indica che una linea di memoria non si trova nel livello L2; data la natura inclusiva della L2, l'ownership è della memoria centrale. Di seguito è riportata uan visione generale degli stati del sistema.

Inoltre si specifica che il nostro protocollo è di tipo invalidate; ciò signifca che ogni volta un core modifica un blocco di memoria deve invalidare gli altri al fine di poter garantire che nessun altro core stia leggendo un valore vecchio di tale blocco in modifica. Infine si suppone che le cache siano di tipo write-back. Ciò significa che i dati vengono scritti in cache e verranno poi scritti in memoria solo quando il dato deve essere rimosso dalla cache stessa.

Lo sviluppo architetturale della cache è basato su tali ipotesi restrittive:

- Se un thread all'interno di un core scatena un cache miss, tale thread è arrestato finchè il controllore di coerenza della cache L1 garantisce le condizioni per poter proseguire l'esecuzione dettate dal protocollo. Tale scelta semplifica l'architettura ed evidenzia la capacità del core di poter eseguire altri calcoli da parte di altri thread attivi, nascondendo le latenze del protocollo di coerenza.

- Non è supportato il merging delle richieste di coerenza da parte di un core.

- E' possibile istanziare solo reti N x N, dove N è una potenza di 2; questo implica l'introduzione di tile vuote che non hanno a disposizione una porzione della cache L2 e directory, a differenza delle tile per il controllo della memoria principale e per la comunicazione con l'host.

Prendendo in considerazione tali assunti e ricordando l'indipendenza tra datapath e controllo di coerenza, lo sviluppo dell'architettura di coerenza si basa su tre attori principali:

- Load Store Unit: contiene la cache L1 e si occupa di gestire la schedulazione delle richieste tra i vari thread del core.

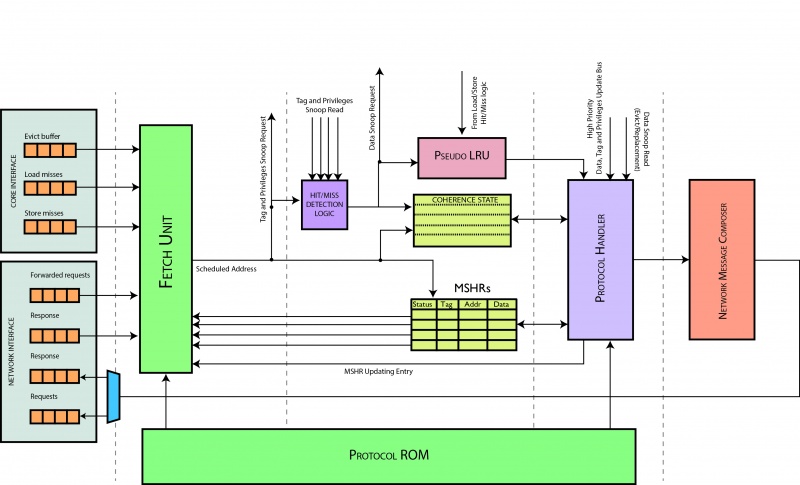

- Cache Controller: gestisce la coerenza dei blocchi della cache livello 1, comunicando direttamente con la Load Store unit ed inviando/ricevendo messaggi di coerenza verso/da altri controllori attraverso una network interface.

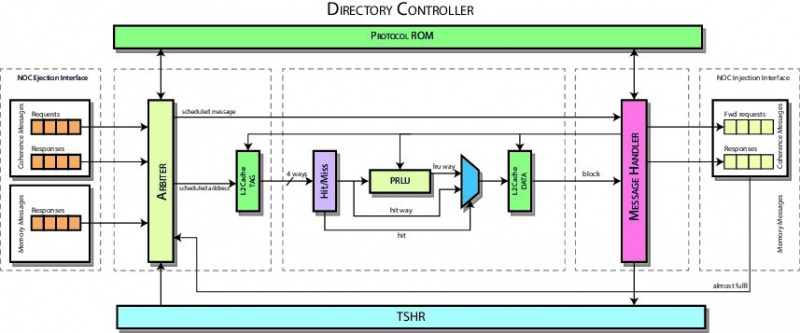

- Directory Controller: contiene e gestisce direttamente la coerenza dei blocchi della cache livello 2 e della cache della directory distribuita, comunicando con gli altri controllori tramite lo scambio di messaggi sulla network attraverso l'opportuna interfaccia.

La Load Store unit ed il Cache controller si trovano all'interno del core nu+, mentre il Directory controller è istanziato all'esterno del core nu+ entro la tile.

L1 cache

The l1 cache bla bla bla

L1 cache controller

This unit is described in the dedicated L1 cache controller page.

Load/Store unit

The \texttt{Load Store Unit} does not store specific coherence protocol information (as stable states) but it stores \textit{privileges} for all cached addresses. Each cache line has two privileges: \textit{can read} and \textit{can write}. Those privileges determine cache misses/hits and are updated only by the \texttt{Cache Controller}. This unit is described in the dedicated load/store unit page.

L2 and directory cache

The l2 cache bla bla bla

This unit is described in the dedicated L2 and Directory cache controller page.